-

利用双输入端的nand门,用Verilog编写自己的与或非门,并用激励模块验证这些门的功能。

-

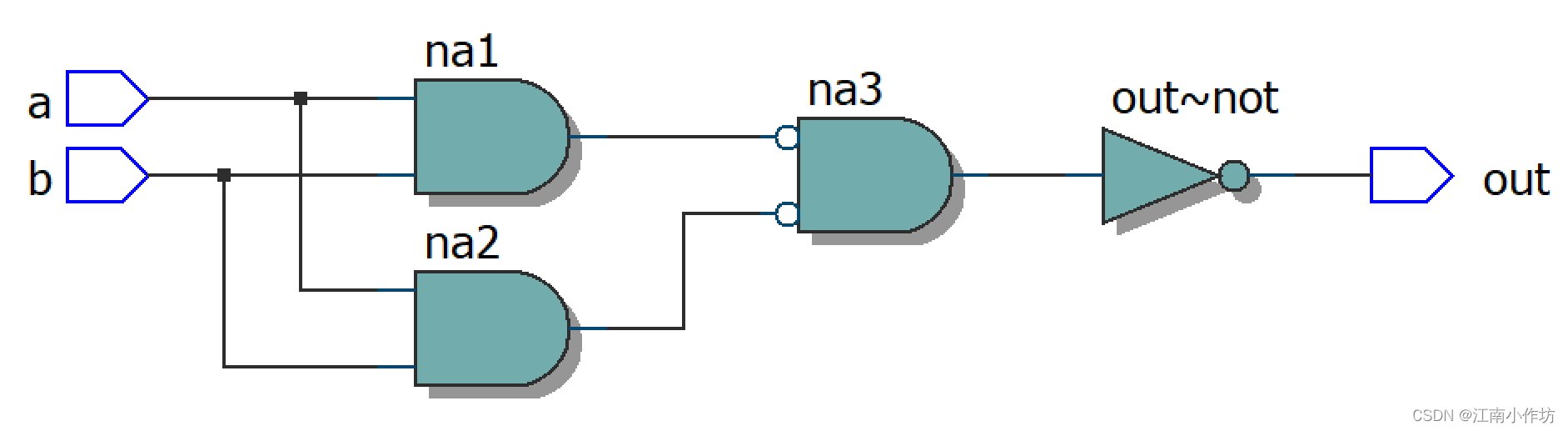

与门,verilog实现,用三个与非门

module my_add(

output out,

input a,

input b

wire w1,w2;

nand na1(w1,a,b);

nand na2(w2,a,b);

nand na3(out,w1,w2);

endmodule

-

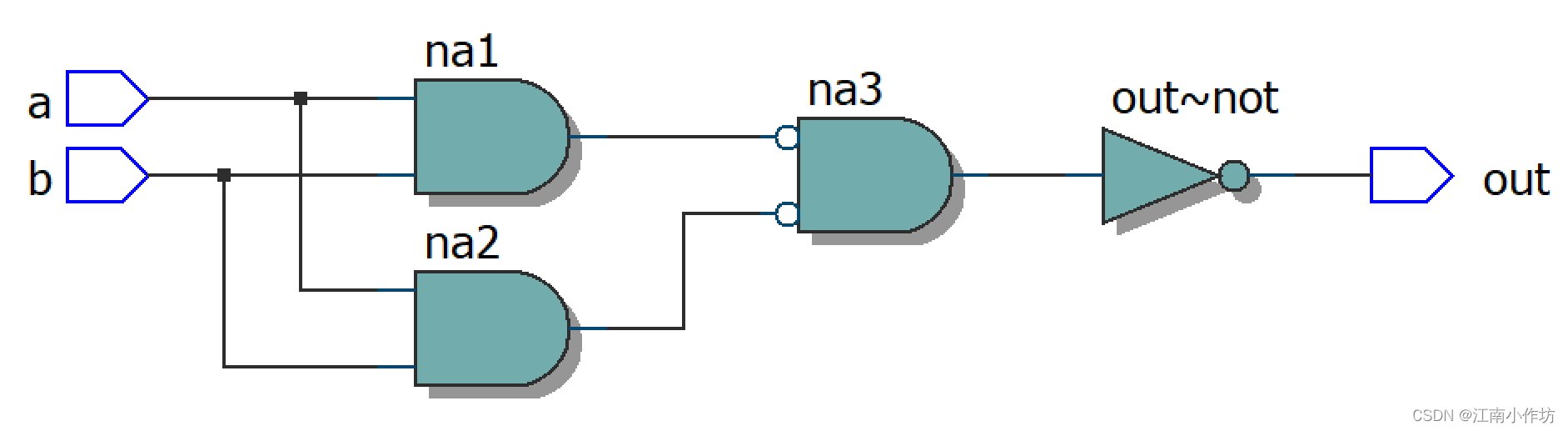

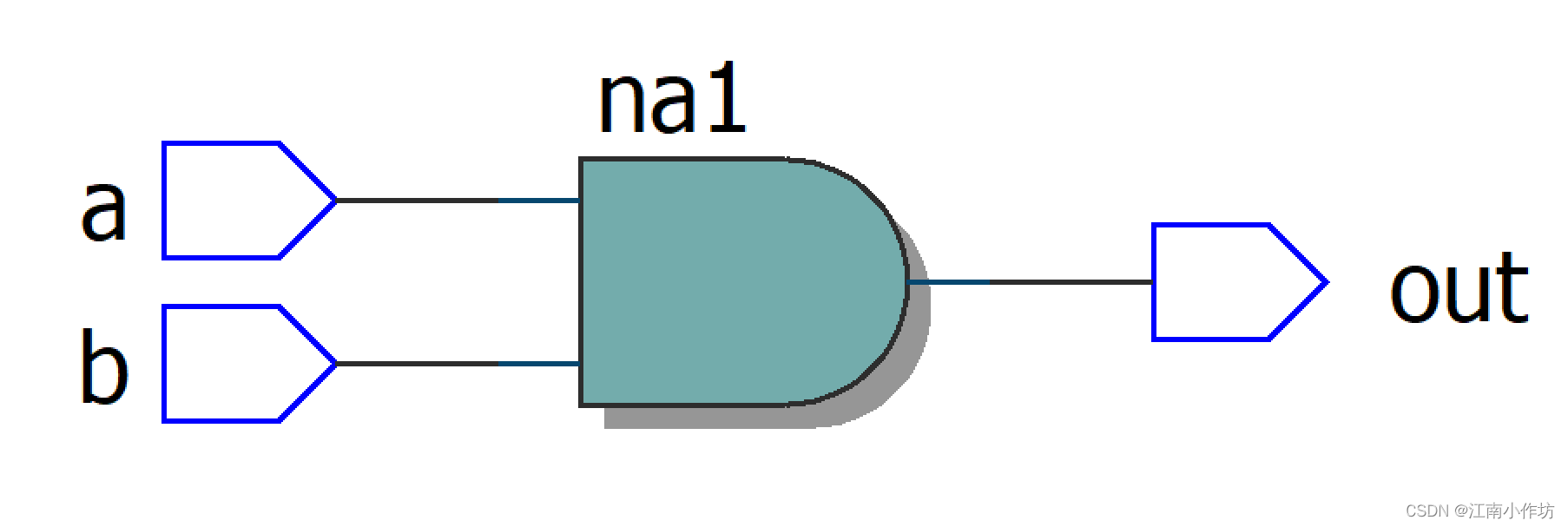

RTL视图

-

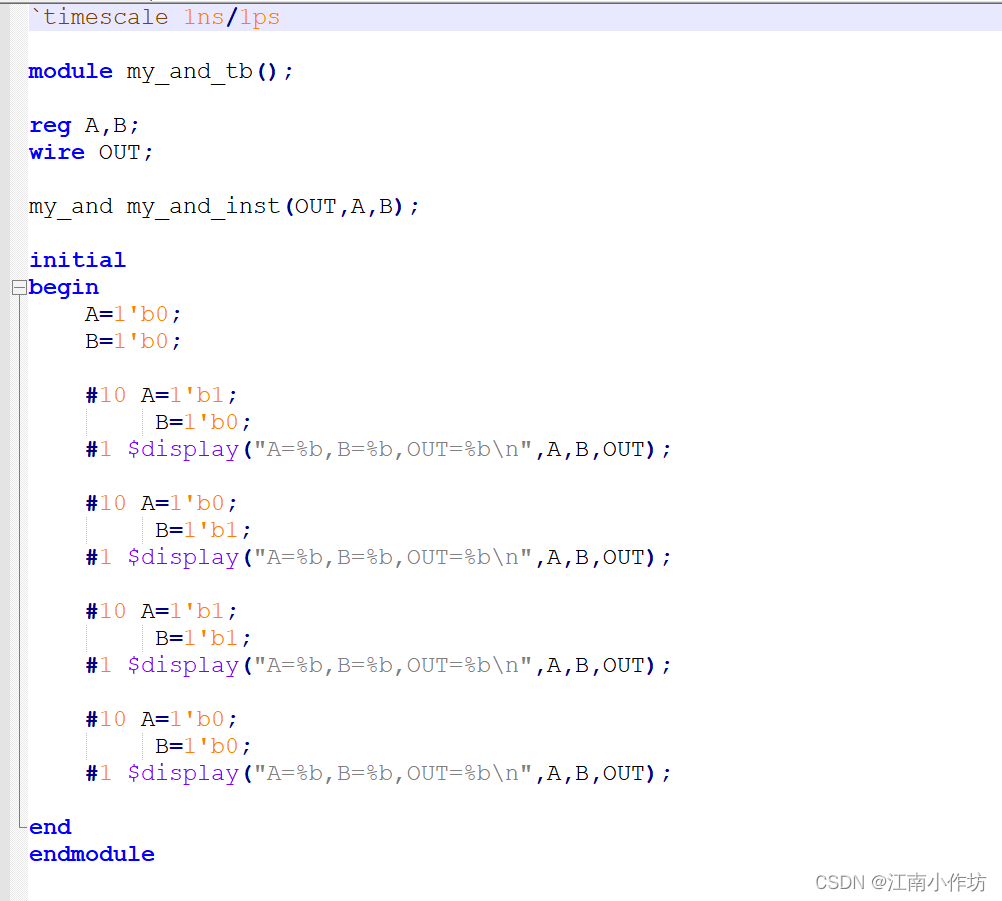

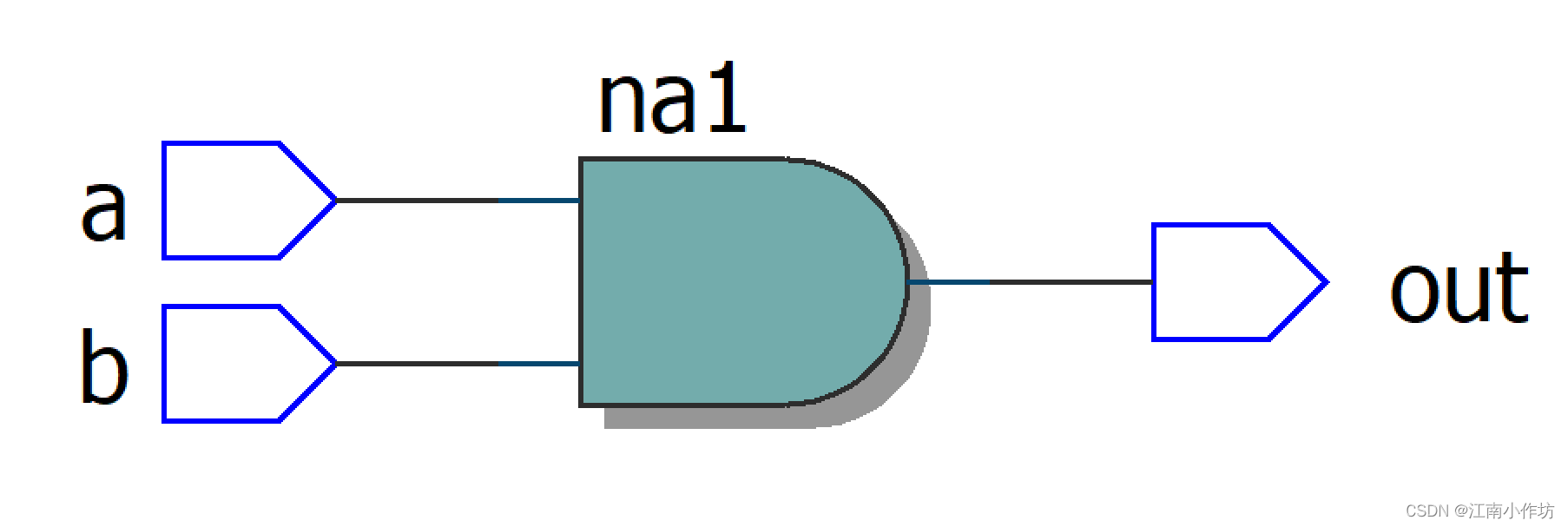

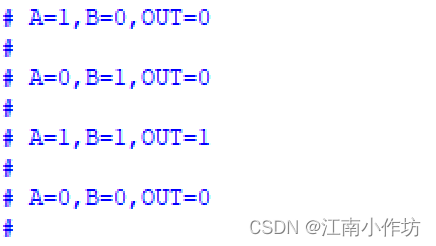

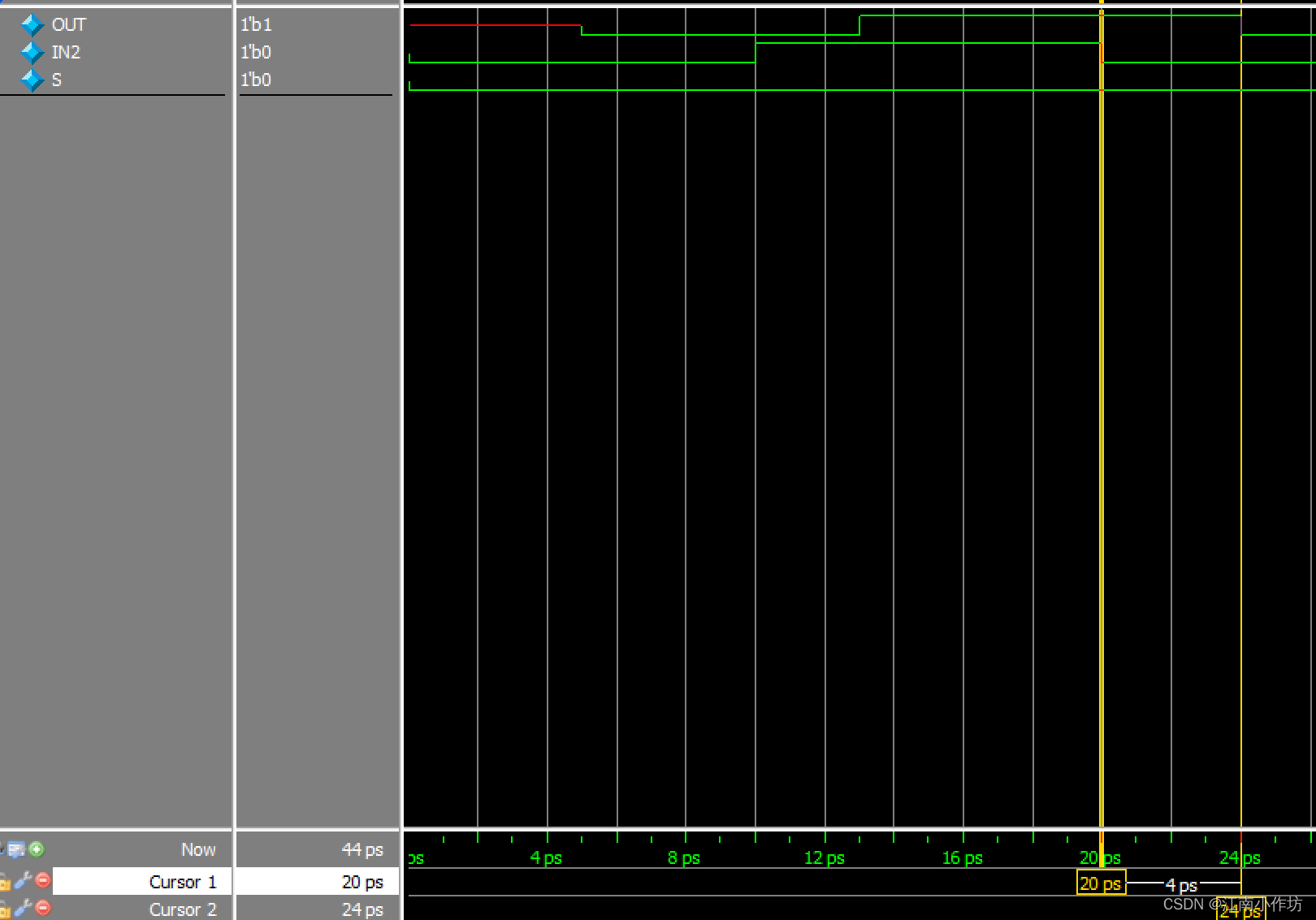

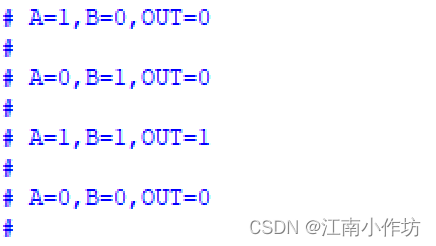

仿真实现

-

仿真结果满足与门逻辑。

-

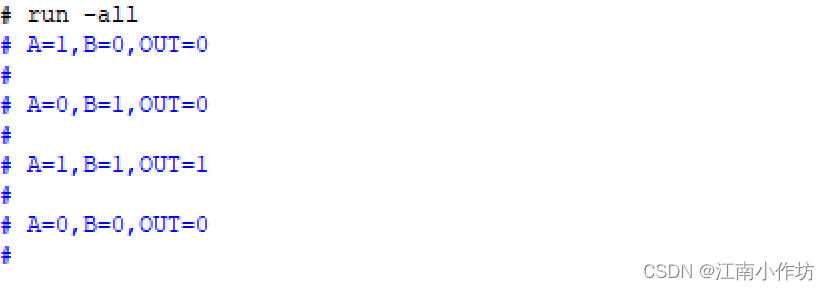

与门(第二种方式),Verilog实现,两个与非门

module my_and(

output out,

input a,

input b

wire w1;

nand na1(w1,a,b);

nand na2(out,w1,w1);

endmodule

-

RTL视图

-

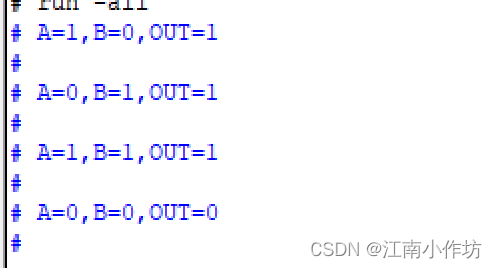

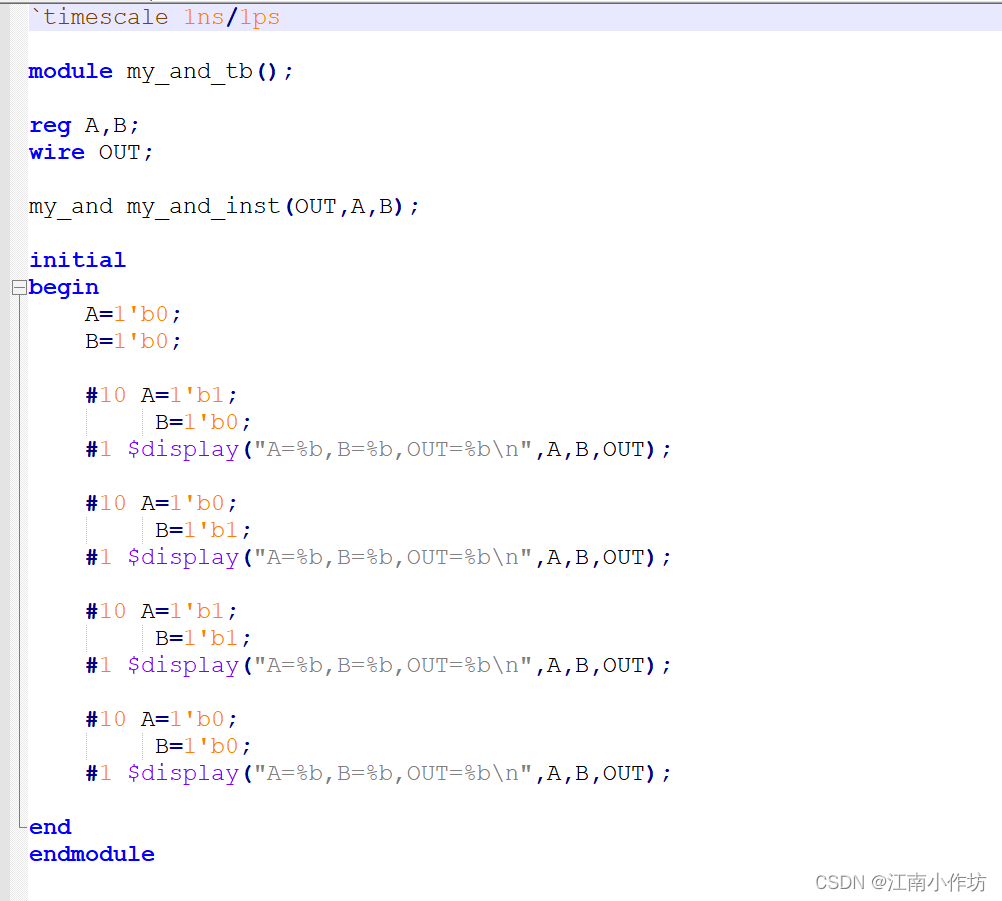

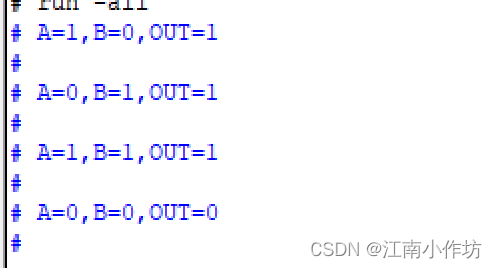

仿真结果

-

或门,verilog实现

module my_or(

output out,

input a,

input b

wire w1,w2;

nand (w1,a,a);

nand (w2,b,b);

nand (out,w1,w2);

endmodule

-

仿真验证

-

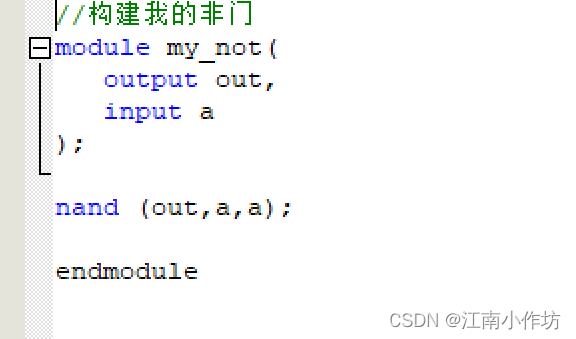

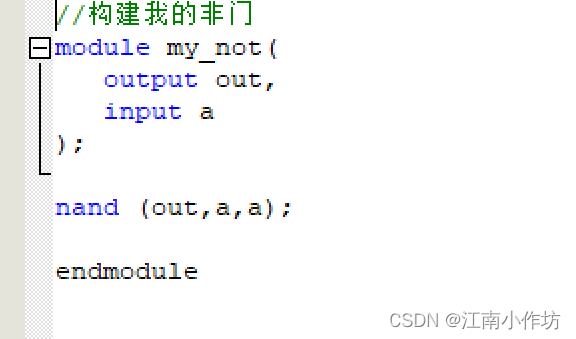

非门,就很简单啦,把与非门输入短接就行啦,就不一一验证了。本来不想写my_not的,结果第二题要用到,贴上其代码。

-

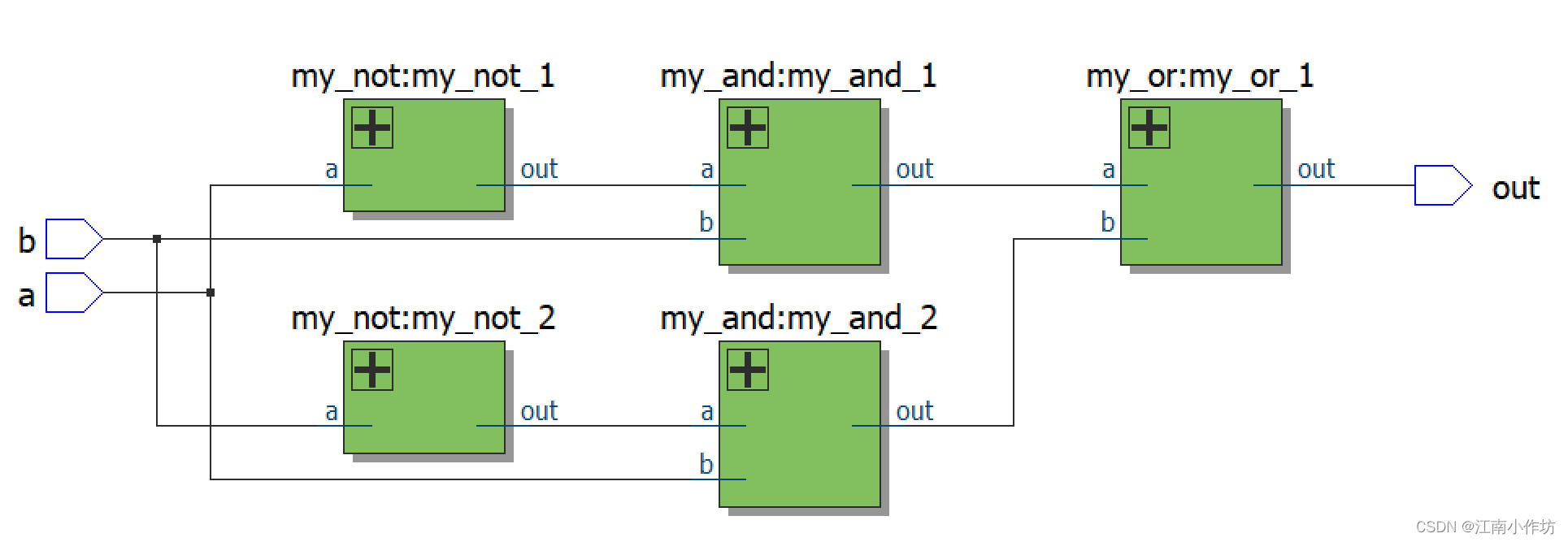

利用上题所定义的my_and,my_or,my_not,来构建一个异或门(xor),功能计算

z

=

x

ˉ

y

+

x

y

ˉ

,编写仿真信号对其测试。

-

verilog实现

module my_xor(

output out,

input a,

input b

wire w1,w2,w3,w4;

my_not my_not_1(w1,a);

my_not my_not_2(w2,b);

my_and my_and_1(w3,w1,b);

my_and my_and_2(w4,w2,a);

my_or my_or_1(out,w3,w4);

endmodule

-

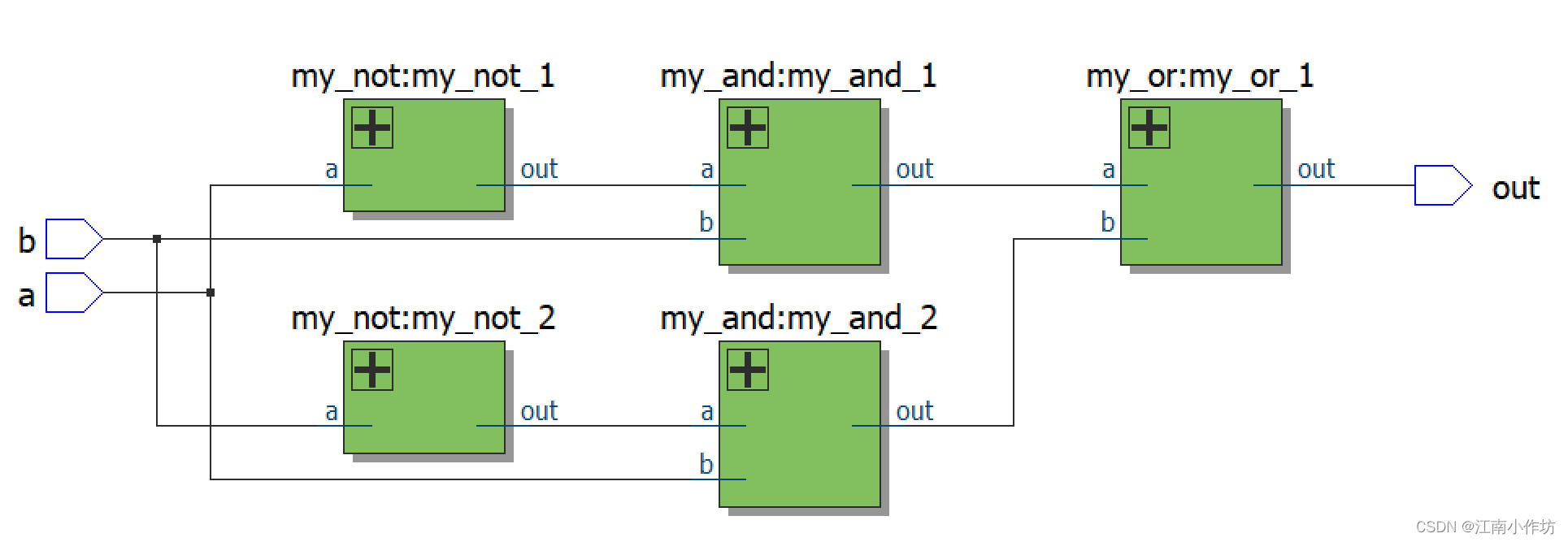

RTL视图

-

仿真设计

module my_xor_tb();

reg x,y;

wire z;

my_xor my_xor_inst(z,x,y);

initial

begin

x=1'b0;

y=1'b1;

#10 x=1'b0;

y=1'b0;

#1 $display("x=%b,y=%b,z=%b\n",x,y,z);

#10 x=1'b0;

y=1'b1;

#1 $display("x=%b,y=%b,z=%b\n",x,y,z);

#10 x=1'b1;

y=1'b0;

#1 $display("x=%b,y=%b,z=%b\n",x,y,z);

#10 x=1'b1;

y=1'b1;

#1 $display("x=%b,y=%b,z=%b\n",x,y,z);

endmodule

-

仿真结果,满足异或门逻辑

-

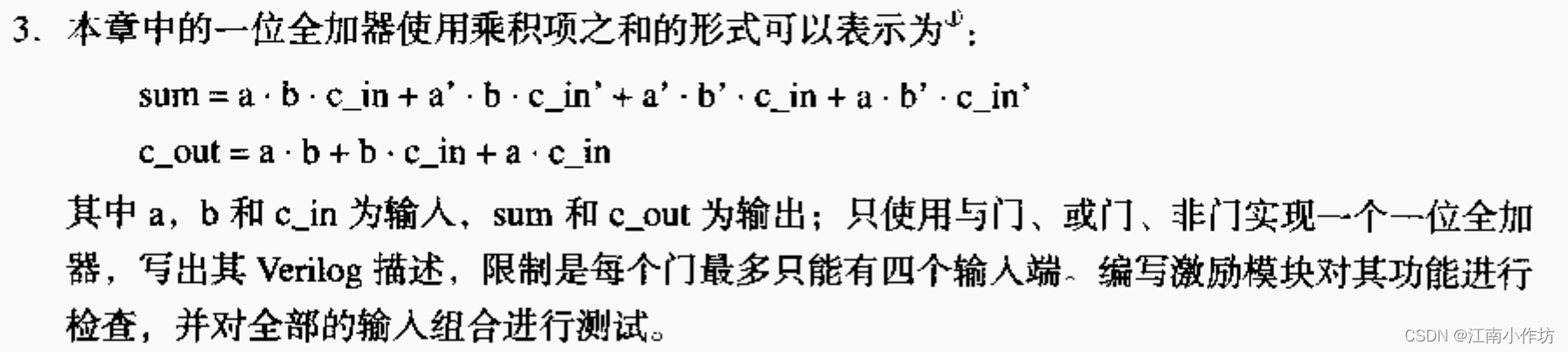

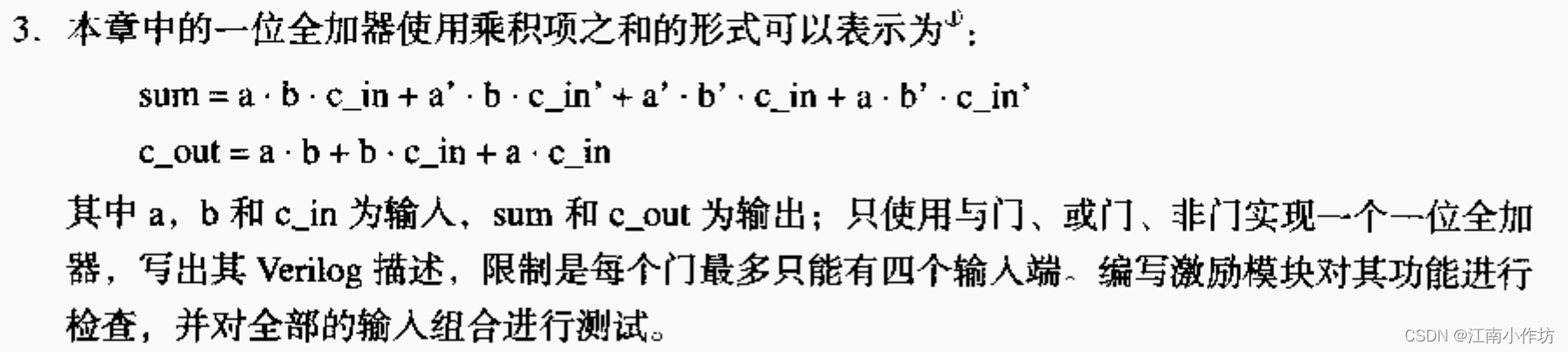

懒得打字拉,题目如下

-

Verilog实现

module my_fulladder(

output sum,

output c_out,

input a,

input b,

input c_in

wire a_1, b_1, c_in_1;

wire s1, s2, s3, s4;

wire c1, c2, c3;

not (a_1, a);

not (b_1, b);

not (c_in_1, c_in);

and (s1,a,b,c_in);

and (s2,a_1,b,c_in_1);

and (s3,a_1,b_1,c_in);

and (s4,a,b_1,c_in_1);

or (sum,s1,s2,s3,s4);

and (c1,a,b);

and (c2,b,c_in);

and (c3,a,c_in);

or (c_out,c1,c2,c3);

endmodule

-

RTL视图

-

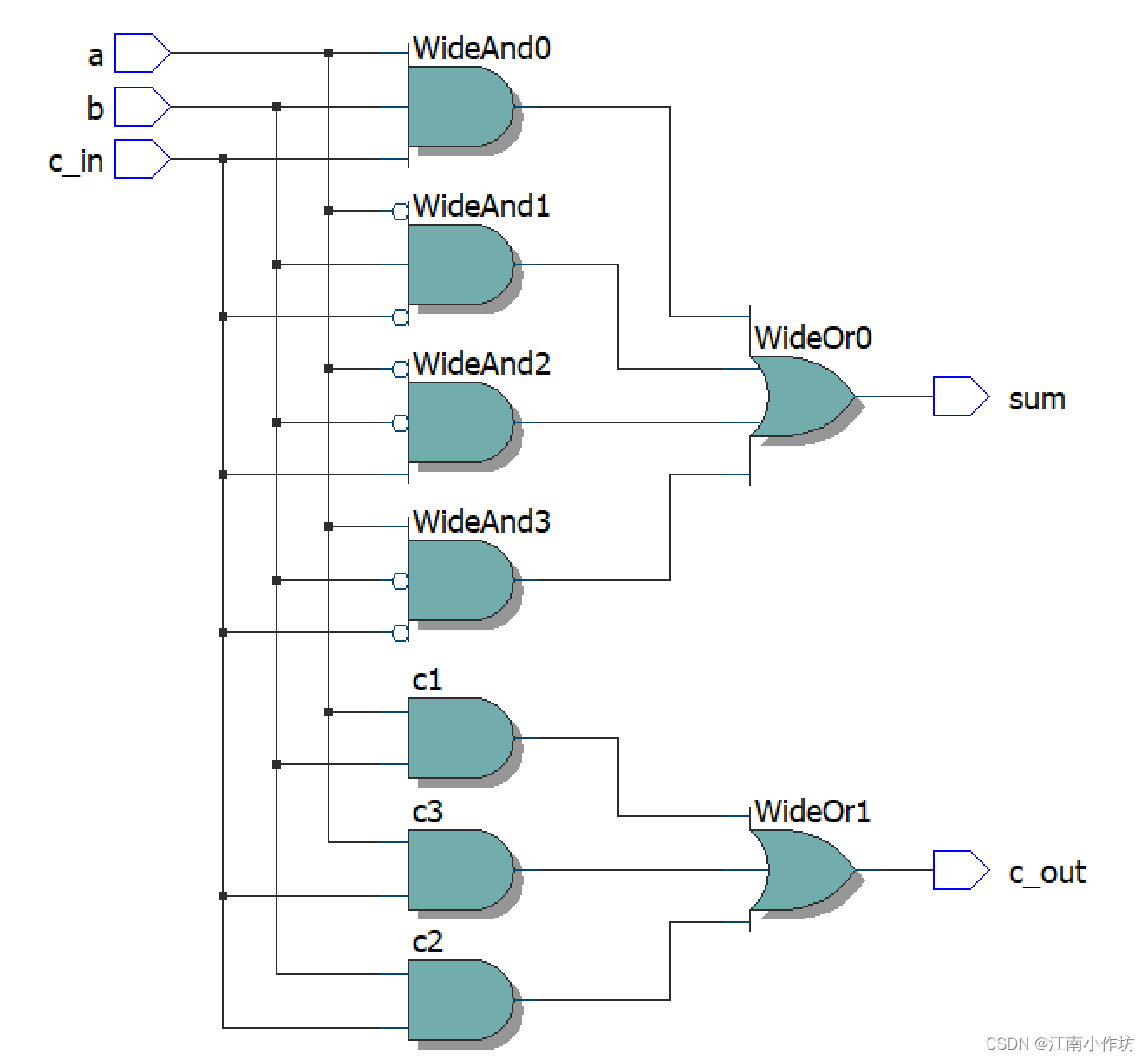

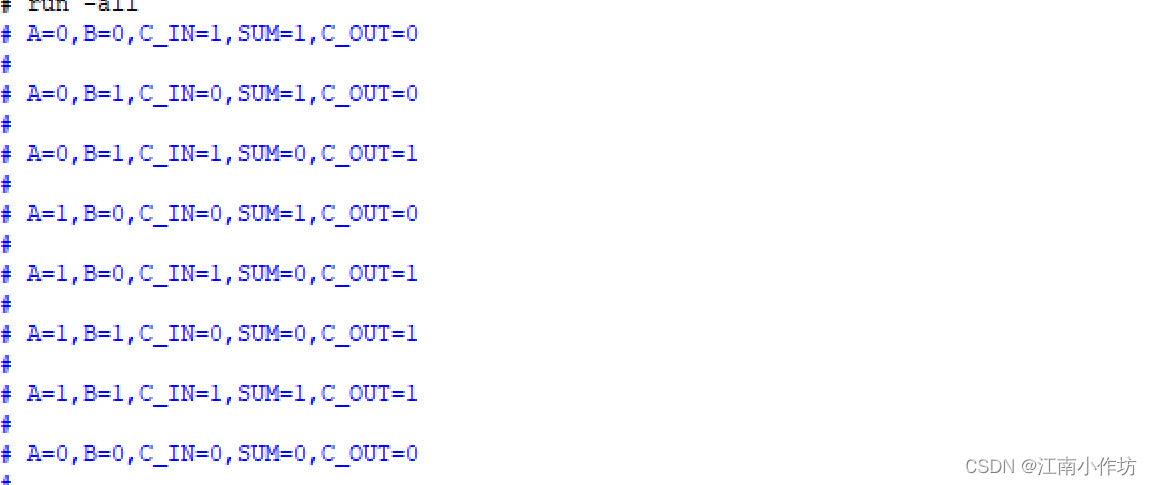

仿真实现

module my_fulladder_tb();

reg A,B,C_IN;

wire C_OUT,SUM;

my_fulladder my_fulladder_inst(SUM, C_OUT, A, B, C_IN);

initial

begin

A = 1'b0;

B = 1'b0;

C_IN = 1'b0;

A = 1'b0;

B = 1'b0;

C_IN = 1'b1;

#1 $display("A=%b,B=%b,C_IN=%b,SUM=%b,C_OUT=%b\n", A, B, C_IN, SUM, C_OUT);

A = 1'b0;

B = 1'b1;

C_IN = 1'b0;

#1 $display("A=%b,B=%b,C_IN=%b,SUM=%b,C_OUT=%b\n", A, B, C_IN, SUM, C_OUT);

A = 1'b0;

B = 1'b1;

C_IN = 1'b1;

#1 $display("A=%b,B=%b,C_IN=%b,SUM=%b,C_OUT=%b\n", A, B, C_IN, SUM, C_OUT);

A = 1'b1;

B = 1'b0;

C_IN = 1'b0;

#1 $display("A=%b,B=%b,C_IN=%b,SUM=%b,C_OUT=%b\n", A, B, C_IN, SUM, C_OUT);

A = 1'b1;

B = 1'b0;

C_IN = 1'b1;

#1 $display("A=%b,B=%b,C_IN=%b,SUM=%b,C_OUT=%b\n", A, B, C_IN, SUM, C_OUT);

A = 1'b1;

B = 1'b1;

C_IN = 1'b0;

#1 $display("A=%b,B=%b,C_IN=%b,SUM=%b,C_OUT=%b\n", A, B, C_IN, SUM, C_OUT);

A = 1'b1;

B = 1'b1;

C_IN = 1'b1;

#1 $display("A=%b,B=%b,C_IN=%b,SUM=%b,C_OUT=%b\n", A, B, C_IN, SUM, C_OUT);

A = 1'b0;

B = 1'b0;

C_IN = 1'b0;

#1 $display("A=%b,B=%b,C_IN=%b,SUM=%b,C_OUT=%b\n", A, B, C_IN, SUM, C_OUT);

endmodule

-

仿真结果,满足设计要求

-

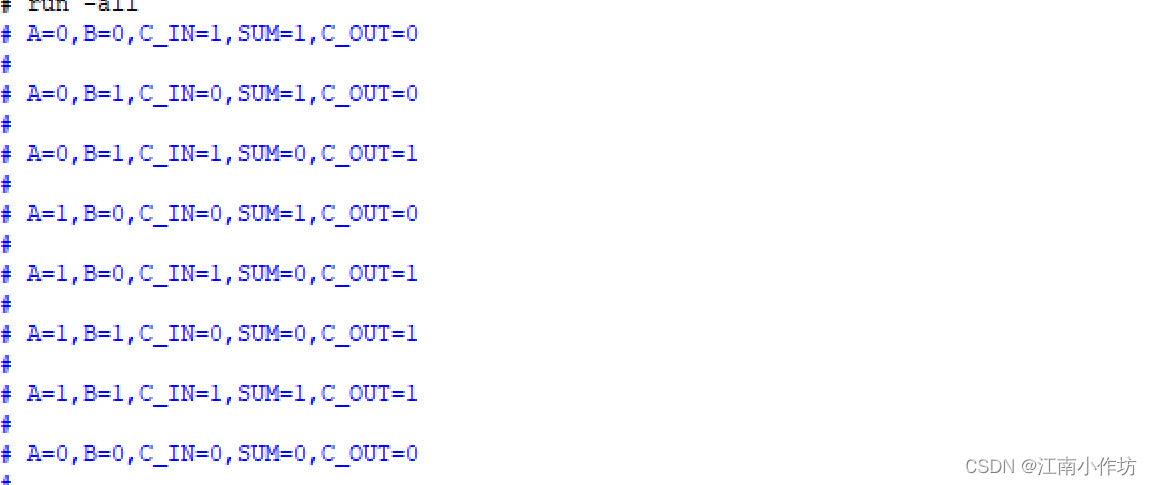

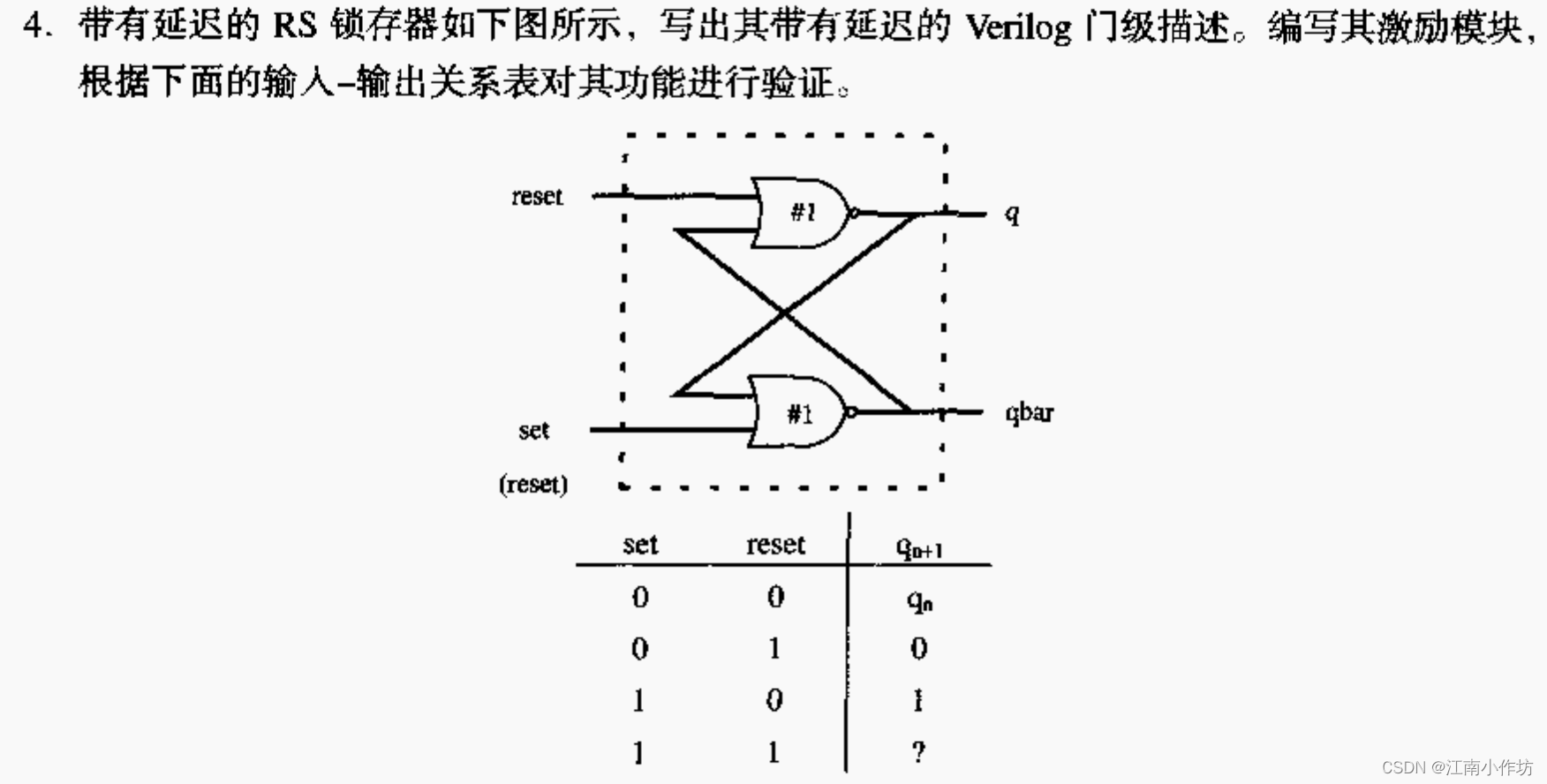

直接上图

-

verilog实现

module my_rs_latch(

output q,

output qbar,

input set,

input reset

nor #(1) (q,reset,qbar);

nor #(1) (qbar,q,set);

endmodule

-

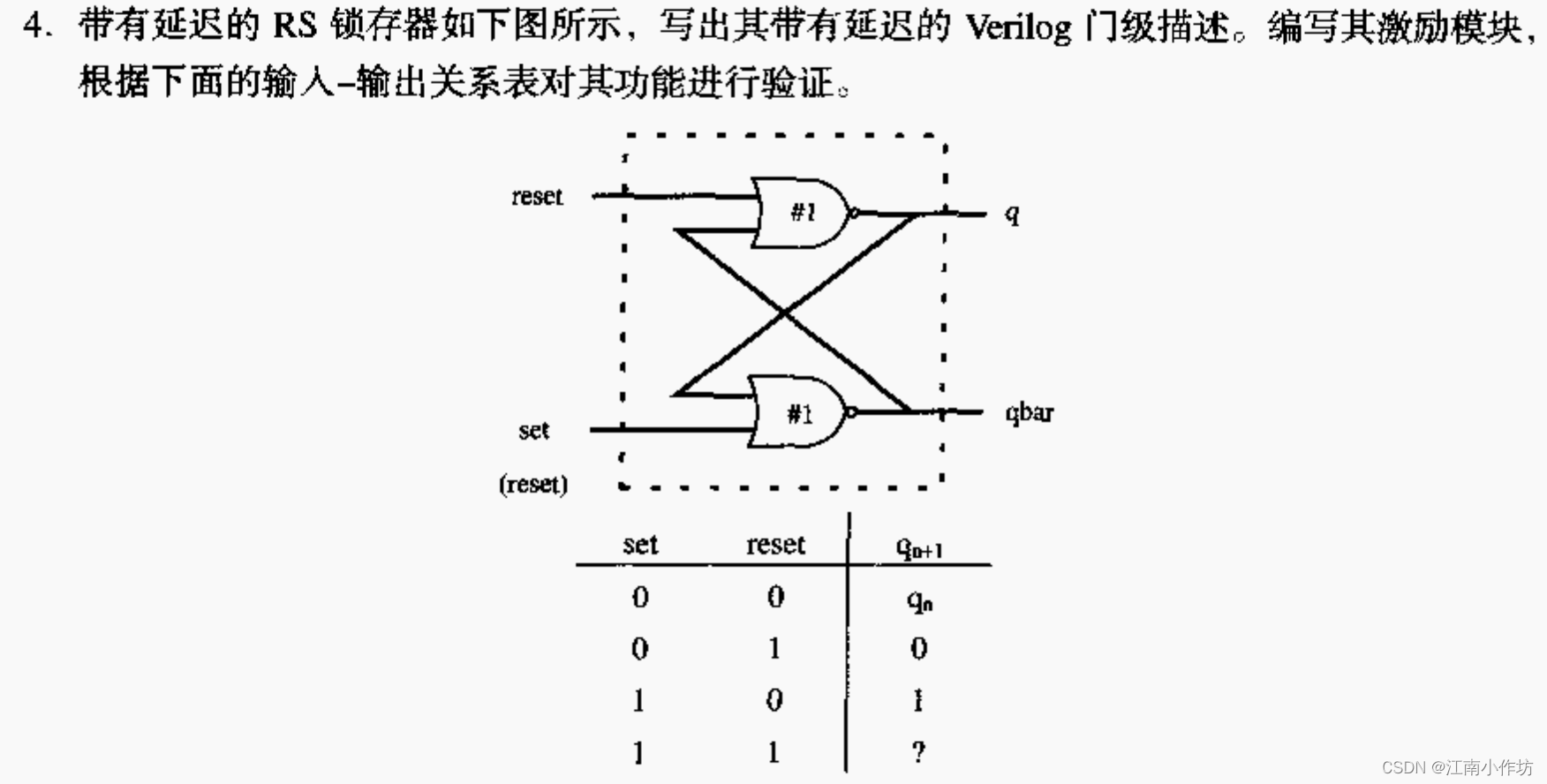

仿真

module my_rs_latch_tb();

reg SET,RESET;

wire Q,QBAR;

my_rs_latch my_rs_latch_inst(Q,QBAR,SET,RESET);

initial

begin

SET=1'b0;

RESET = 1'b0;

SET=1'b0;

RESET = 1'b1;

SET=1'b1;

RESET = 1'b0;

SET=1'b1;

RESET = 1'b1;

endmodule

-

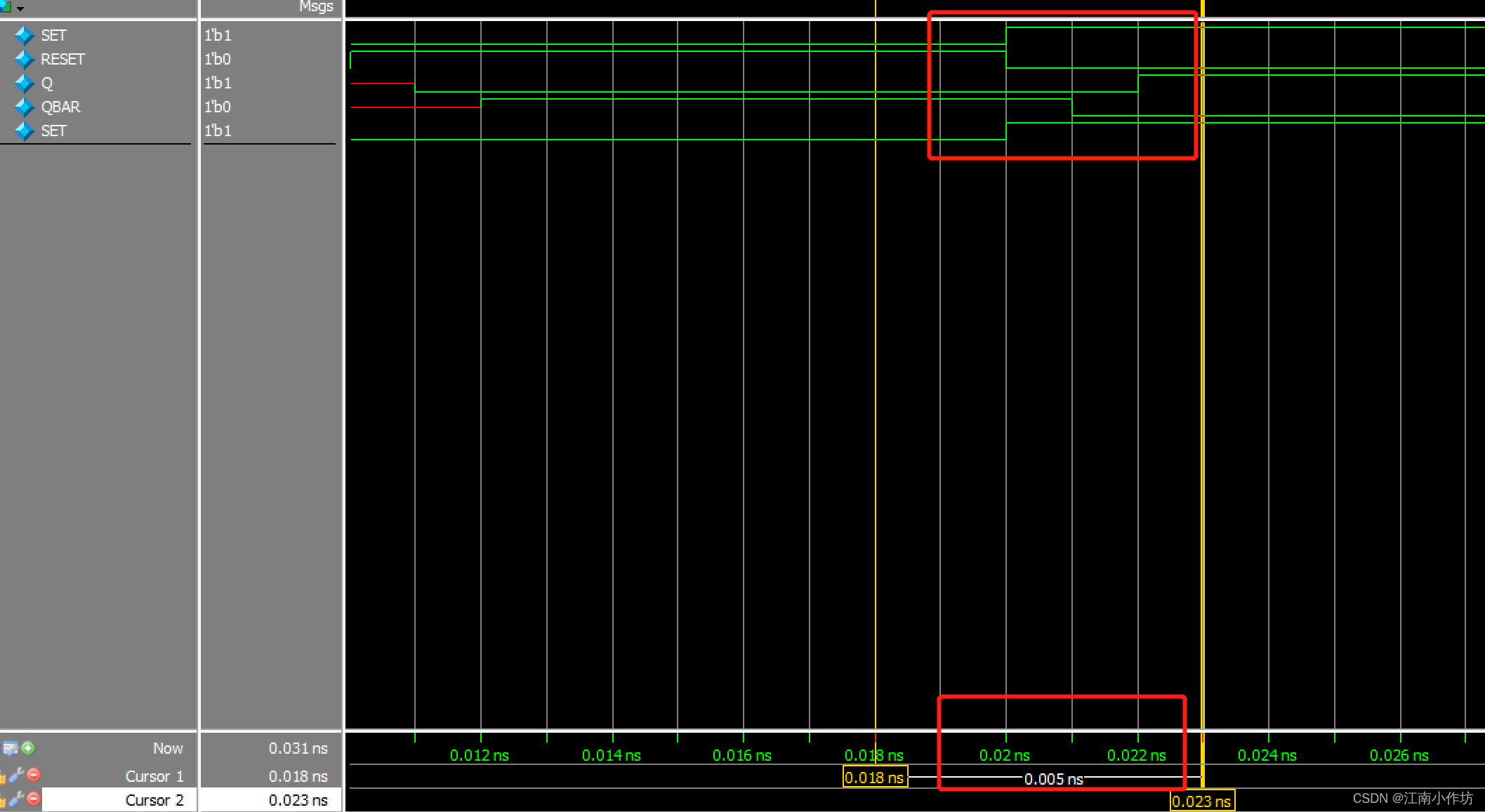

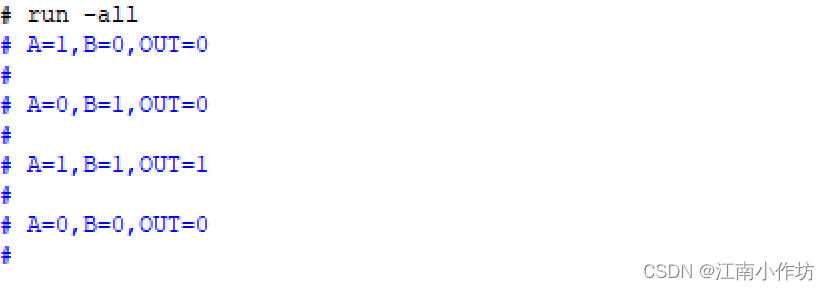

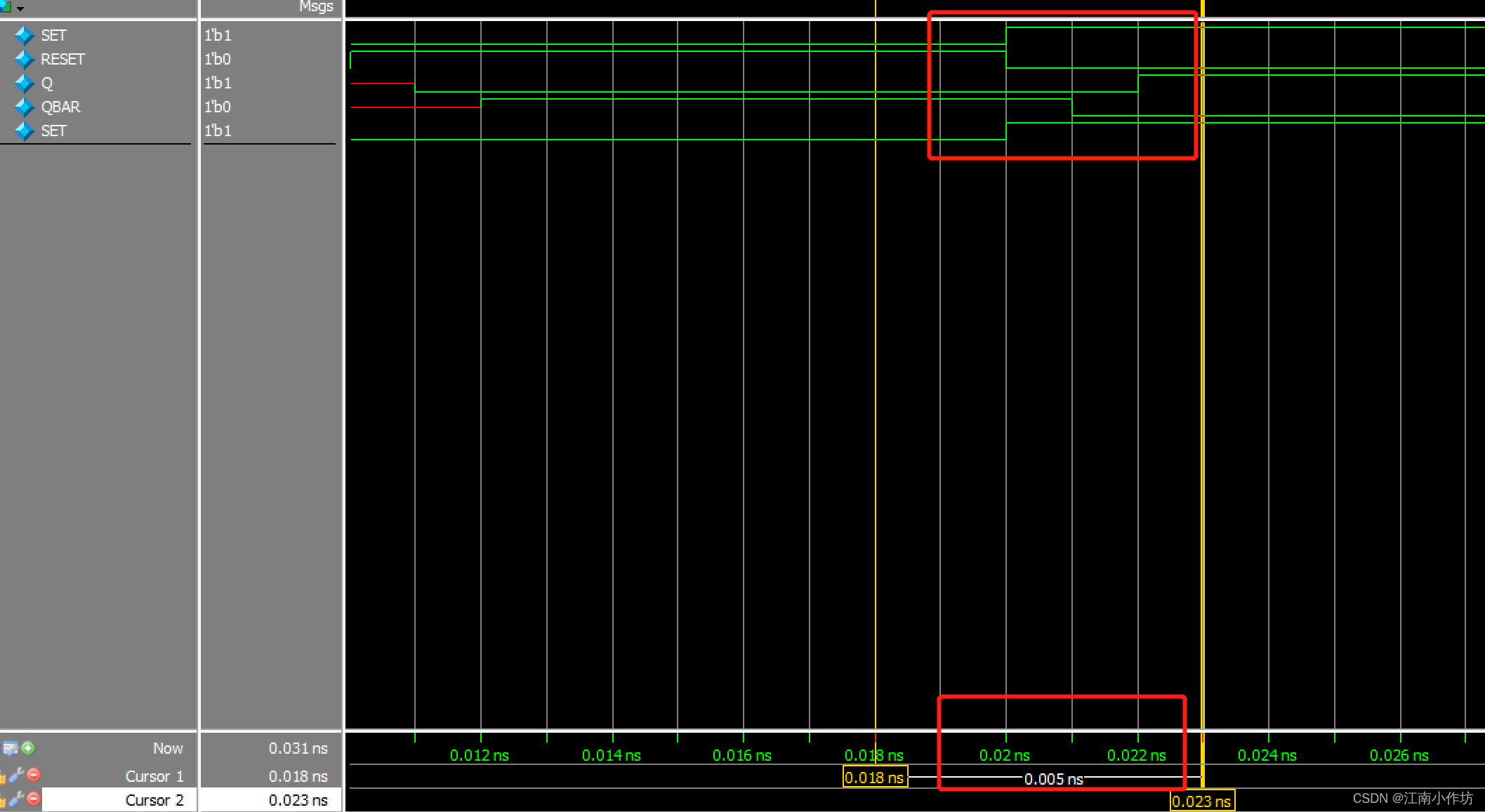

仿真结果,经过两个时间单位(2 ps),q发生改变

-

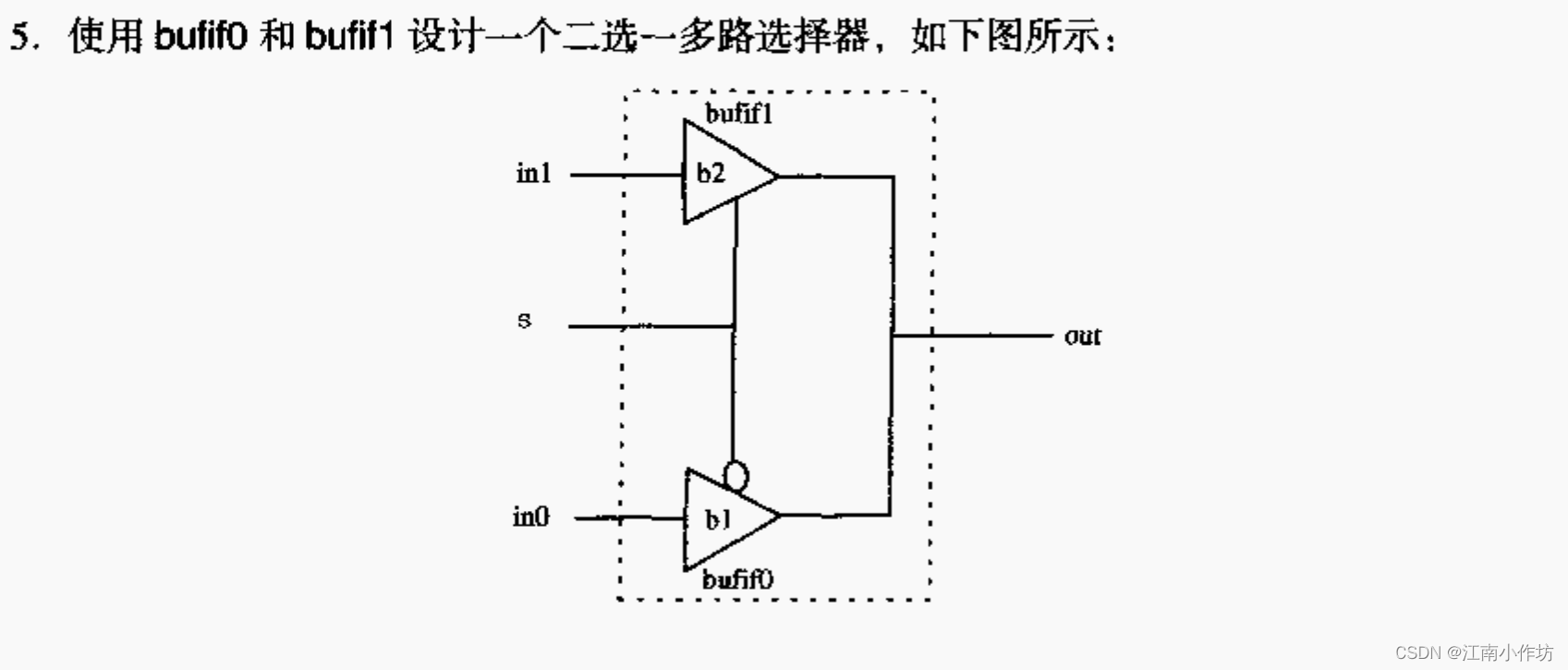

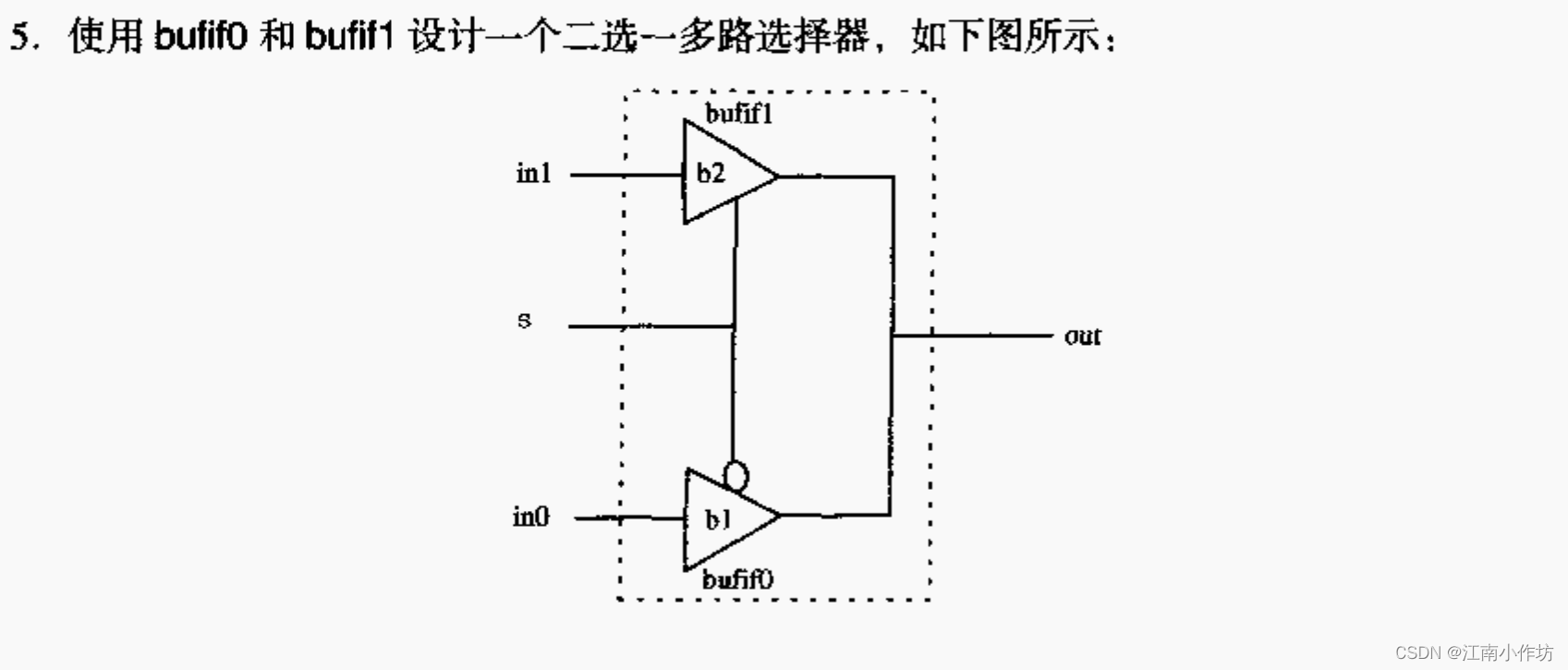

上图

-

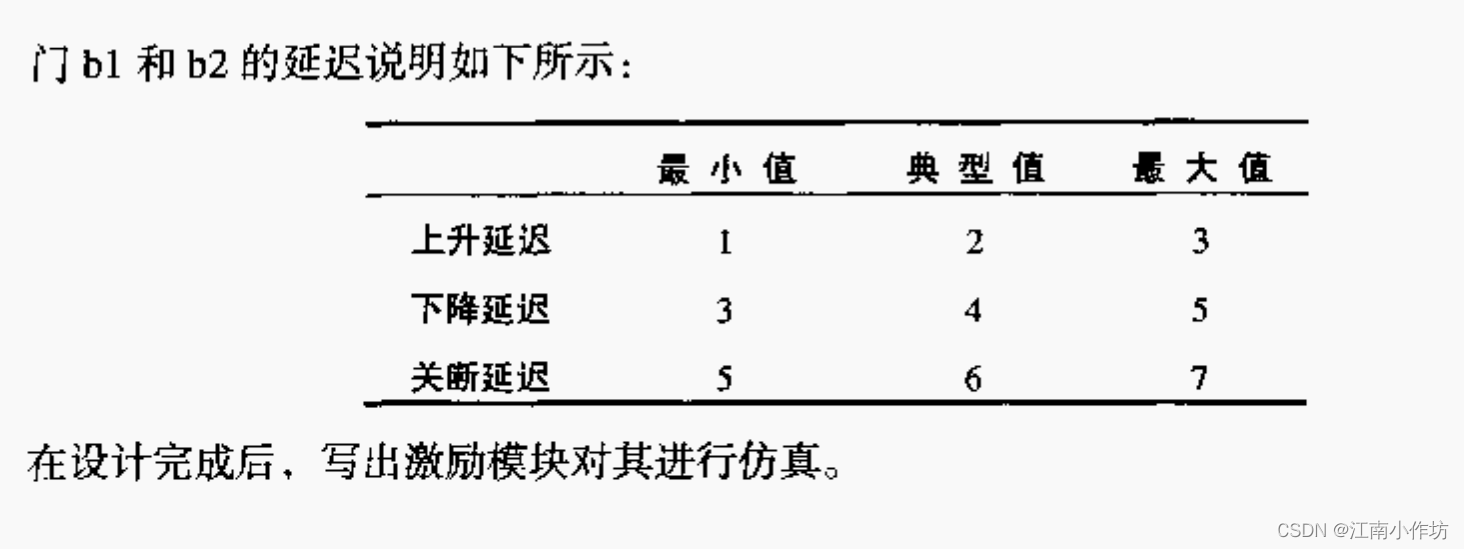

此多路选择器,当s为1的时候,输出in1;s为0的时候,输出in2。

-

verilog实现

module my_mux2_to_1(

output out,

input in1,in2,

input s

bufif1 #(1:3:5,2:4:6,3:5:7) buf1(out,in1,s);

bufif0 #(1:3:5,2:4:6,3:5:7) buf0(out,in2,s);

endmodule

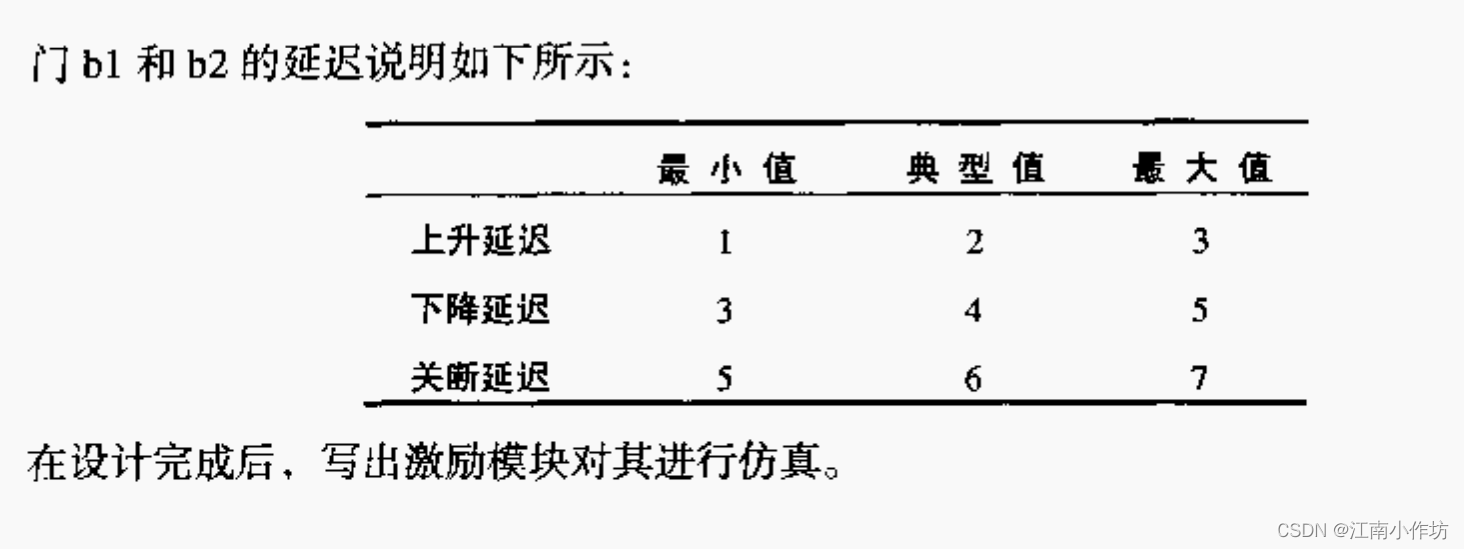

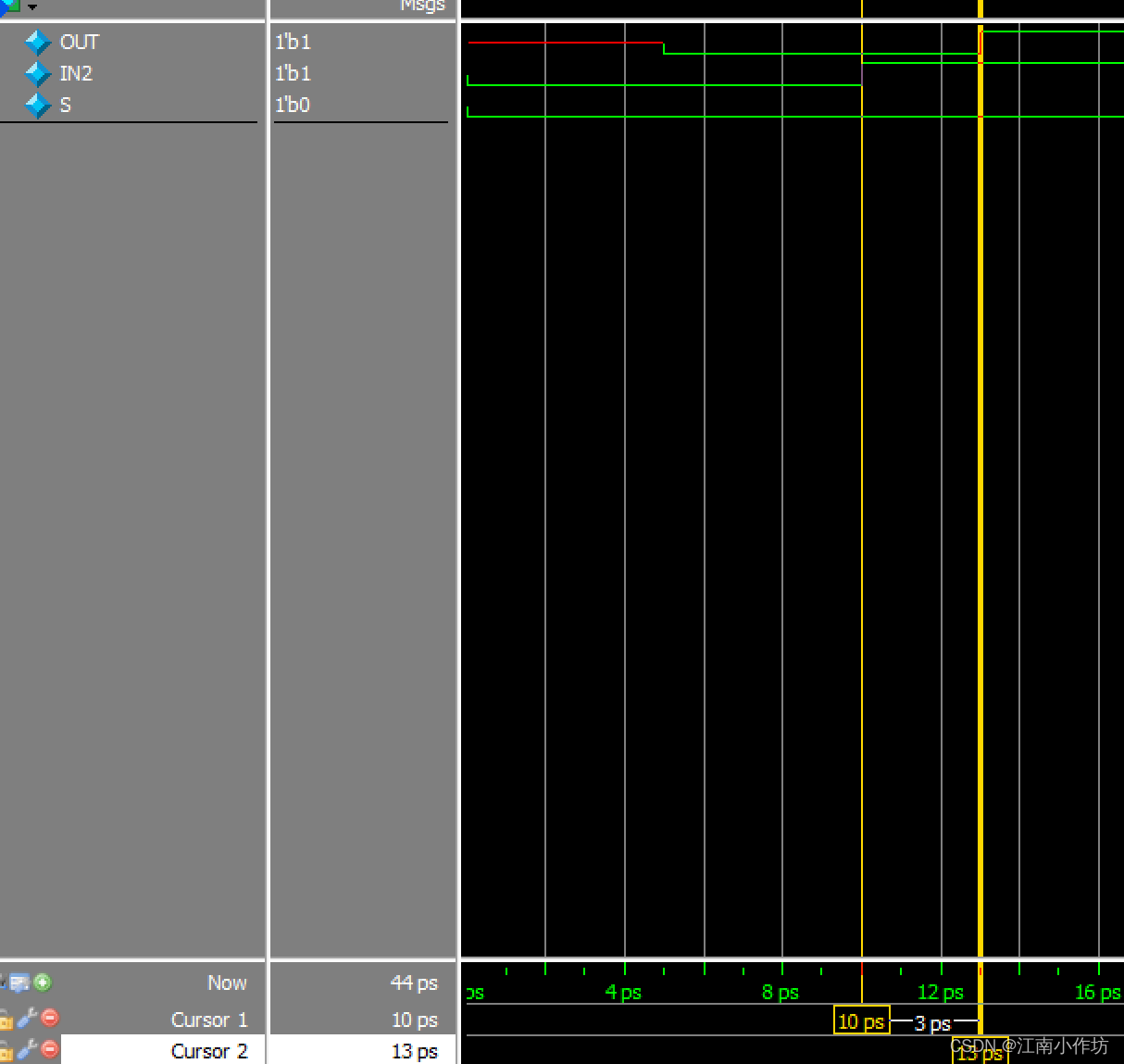

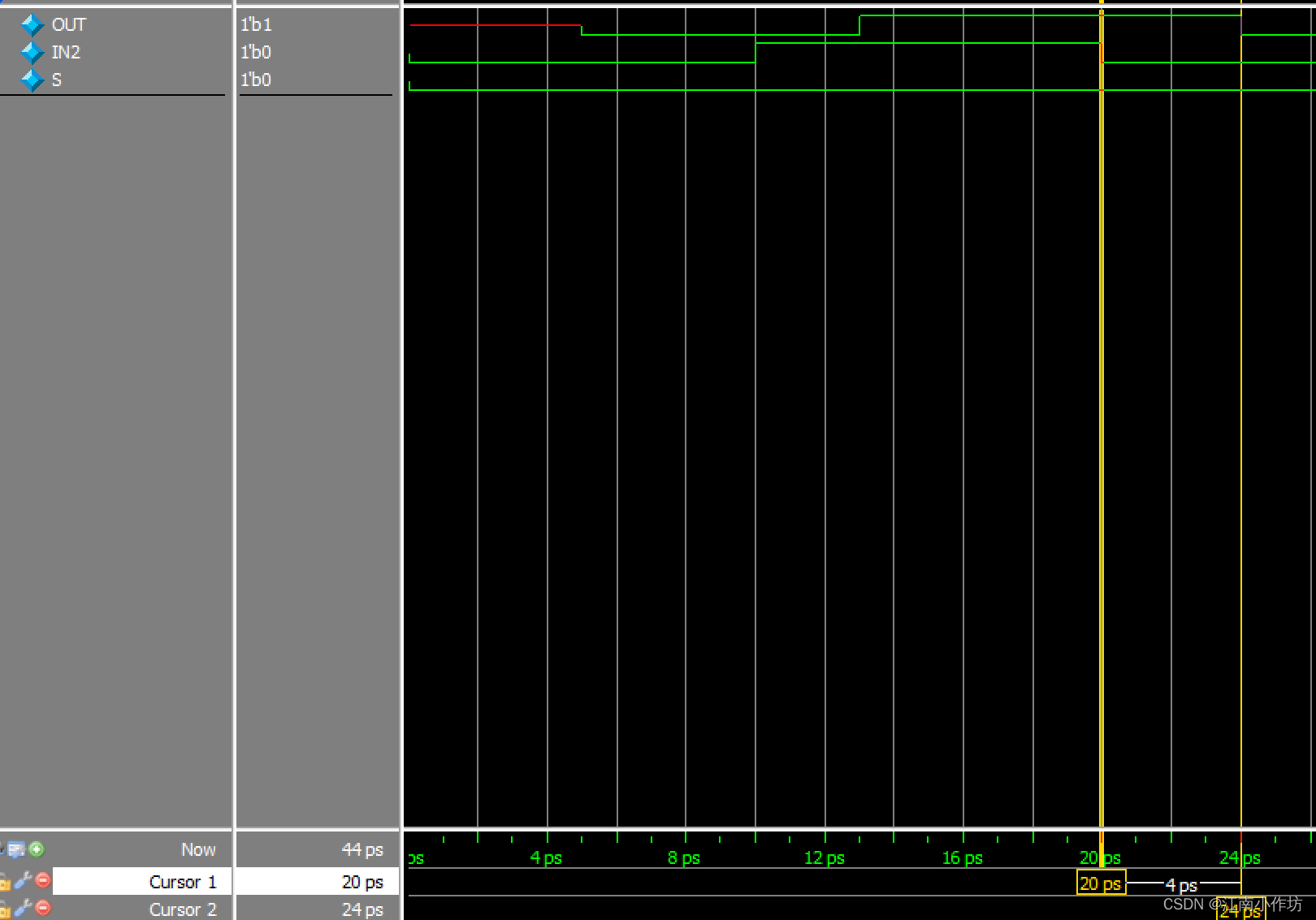

- 当s为0时,输出in2,当in2为1时,延时了3个时间单位后,in2为1

- 当s为0时,输出in2,当in2为0时,延时了4个时间单位后,in2为0

- 当s为1时,同理。