`timescale 1ns/1ns

module test ;

reg rstn ;

reg clk ;

reg [3:0] cnt ;

wire cout ;

counter10 u_counter (

.rstn (rstn),

.clk (clk),

.cnt (cnt),

.cout (cout));

initial begin

clk = 0 ;

rstn = 0 ;

#10 ;

rstn = 1'b1 ;

wait (test.u_counter.cnt_temp == 4'd4) ;

@(negedge clk) ;

force test.u_counter.cnt_temp = 4'd6 ;

force test.u_counter.cout = 1'b1 ;

#40 ;

@(negedge clk) ;

release test.u_counter.cnt_temp ;

release test.u_counter.cout ;

initial begin

clk = 0 ;

forever #10 clk = ~ clk ;

always begin

#1000;

if ($time >= 1000) $finish ;

endmodule

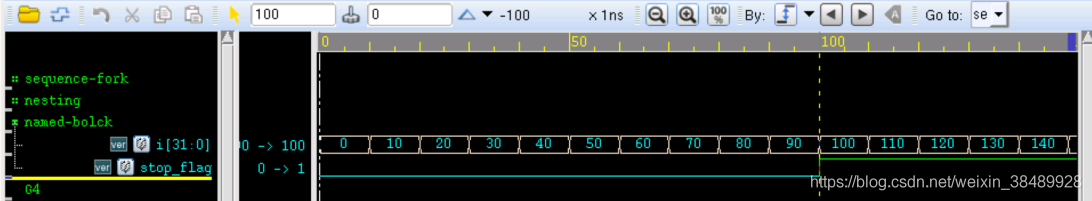

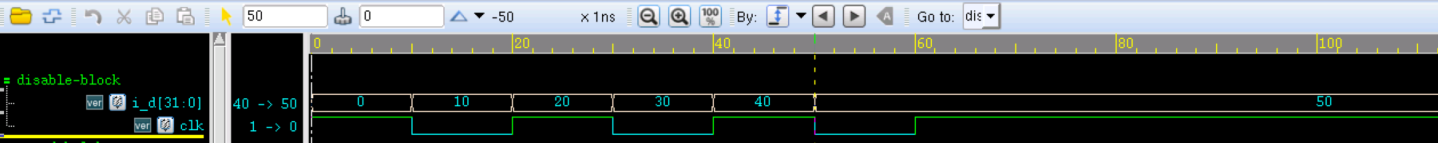

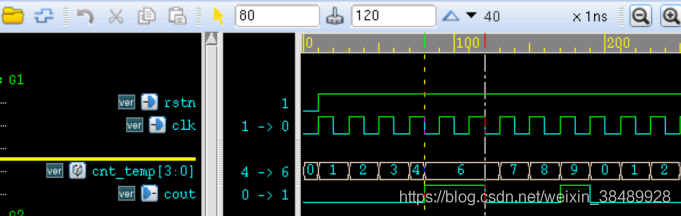

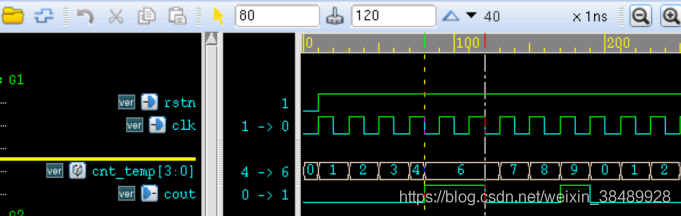

仿真结果如下。

由图可知,在 cnt_temp 等于 4 时(80ns), cnt_temp 被强制赋值为 6,cout 被强制赋值为 1。

release 时(120ns), cnt_temp 为寄存器类型,仍然保持原有值不变,直到时钟上升沿对其进行加法赋值操作,值才变为 7 。

而 120ns 时,由于 cout 是线网型变量,其值不能保存。原码 counter10 模型中存在驱动语句: assign cout = (cnt_temp==4’d9) ,所以 cout 值变为 0 。

文章目录4.1 Verilog 条件语句if 语句4.2 Verilog 多路分支语句case语句casex/casez 语句4.3 Verilog 循环语句while 循环for 循环repeat 循环forever 循环4.4 Verilog 过程连续赋值assign, deassignforce, release4.1 Verilog 条件语句if 语句条件(if)语句用于控制执行语句要根据条件判断来确定是否执行。条件语句用关键字 if 和 else 来声明,条件表达式必须在圆括号中。条件

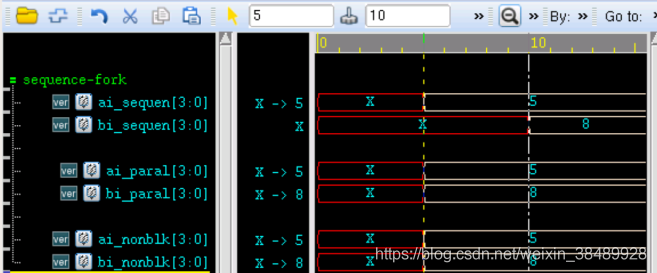

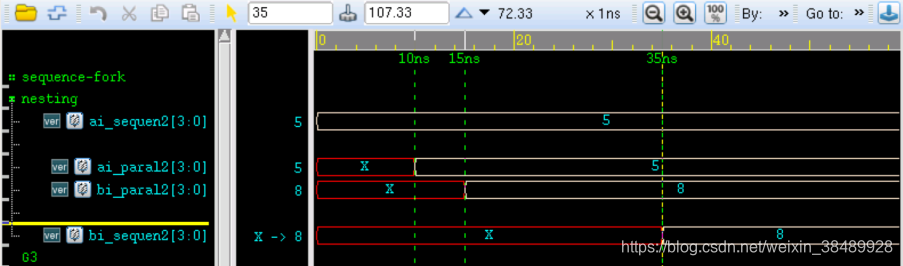

7.2 顺序语句块语句块块提供将两条或更多条语句组合成语法结构上相当于一条语句的机制。这里主要讲Verilog HDL 的顺序语句块(begin . . . end) :语句块中的语句按给定次序顺序执行。顺序语句块中的语句按顺序方式执行。每条语句中的时延值与其前面的语句执行的模拟时间相关。一旦顺序语句块执行结束,跟随顺序语句块过程的下一条语句继续执行。顺序语句块的语法如下: begin[ :block_id{declarations} ]procedural_statement ( s ) end 例如:/ / 产生波形:begin #2 Stream = 1;#5 Stream = 0;#

文章目录2.1 Verilog 基础语法格式注释标识符与关键字2.2 Verilog 数值表示数值种类整数数值表示方法实数表示方法字符串表示方法2.3 Verilog 数据类型线网(wire)寄存器(reg)向量整数,实数,时间寄存器变量2.4 Verilog 表达式表达式操作数操作符算术操作符关系操作符等价操作符逻辑操作符按位操作符归约操作符移位操作符拼接操作符条件操作符

2.1 Verilog 基础语法

Verilog 是区分大小写的。

格式自由,可以在一行内编写,也可跨多行编写。

每个语句必须

结构建模方式有 3 类描述语句: Gate(门级)例化语句,UDP (用户定义原语)例化语句和 module (模块) 例化语句。本次主要讲述使用最多的模块级例化语句。

文章目录5.1 Verilog 模块与端口模块端口inout 端口仿真5.2 Verilog 模块例化命名端口连接顺序端口连接端口连接规则

5.1 Verilog 模块与端口

模块是 Verilog 中基本单元的定义形式,是与外界交互的接口。

模块格式定义如下:

module module_name

#(parameter_l

文章目录3.1 Verilog 连续赋值assign 语句连续赋值时延全加器3.2 Verilog 过程结构、赋值和时序控制Verilog 过程结构initial语句always 语句Verilog 过程赋值阻塞赋值非阻塞赋值使用非阻塞赋值避免竞争冒险Verilog 过程时序控制时延控制常规时延内嵌时延事件控制边沿触发事件控制电平敏感事件控制

3.1 Verilog 连续赋值

assign 语句

连续赋值语句是 Verilog 数据流建模的基本语句,用于对 wire 型变量进行赋值。格式如下:

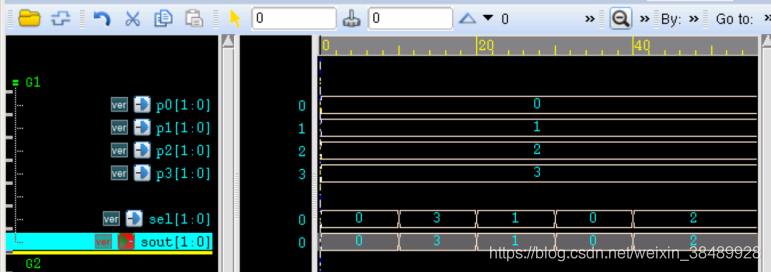

在这个例子中,`data`是一个4位输入,`sel`是一个2位输入,`out`是一个输出。根据`sel`的值,选择对应的输入数据并将其赋值给`out`。如果`sel`的值不在0-3之间,则将`out`赋值为高阻态(`1'bz`)。

请注意,这只是一个简单的示例代码,实际情况可能会有所不同。具体实现方式可能因项目要求和设计约束而有所变化。